ハードウェアトレース¶

Note

SOLID 2.2.0 以降で使用できます。

概要¶

ARMプロセッサの ETB または ETR ユニットの機能を使用し、命令トレースを取得・表示します。

- ETBトレース

CPU内蔵のトレース専用メモリにトレース情報を保存します。ターゲットの動作パフォーマンスに影響を与えませんが、保存可能なサイズが少ないというデメリットがあります。 利用可能な内蔵メモリのサイズはターゲットに依存しますが、一般的に8KBから64KB程度です。

- ETRトレース

ターゲットのRAM上にトレース情報を保存します。使用するサイズを指定可能で、ETBトレースと比べて大きなサイズのメモリを確保できます。 ただし、メモリバスを占有し、システムのパフォーマンスに大きな影響を与える可能性があります。また、メモリ帯域の問題でトレースデータのオーバーフローが多発する可能性があります。

利用可能なターゲット¶

ETBトレースを使用するには、SoCにETB(ETF)ユニットが搭載されている必要があります。

ETRトレースを使用するには、SoCにETRユニットが搭載されている必要があります。

準備¶

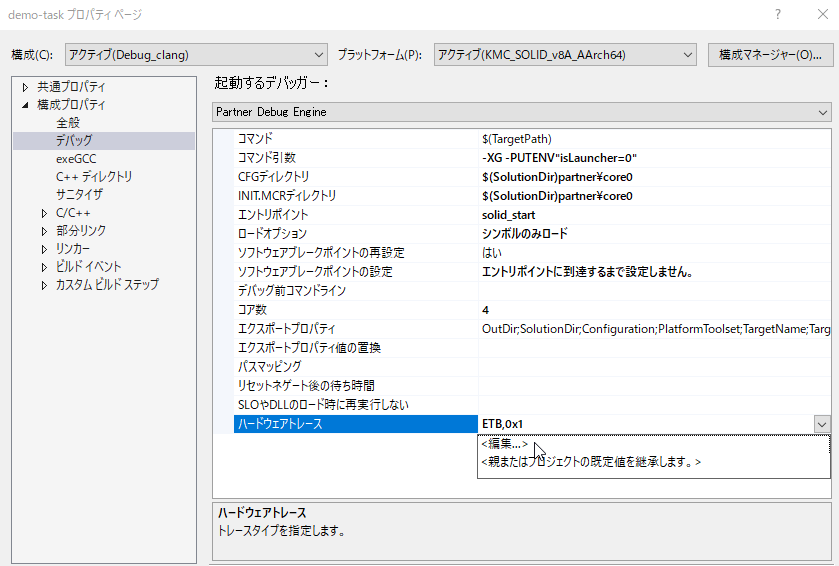

デバッガコンフィグ (

jetarm.cfg) のROMテーブル設定 (CS_ROM_TBL) に、必要なCoreSightコンポーネントのアドレスが正しく記述してください。ETBを使用する場合は、ETM/ETB(ETF)/Funnel の設定が必要です。

ETRを使用する場合は、ETM/ETR/Funnelの設定が必要です。

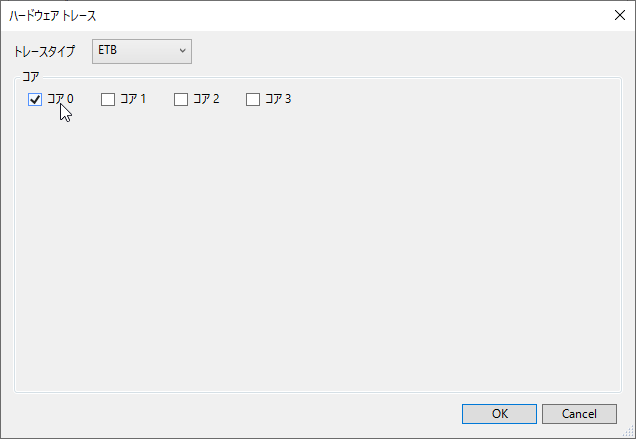

ETBの設定¶

プロジェクトのプロパティを開き を編集します。

ハードウェアトレースの設定ダイアログで、 トレースタイプ を ETB に設定し、取得したいコアにチェックを入れます。

Note

ETBはトレースメモリが小さいため、複数コアを同時に選択すると目的の範囲のトレースを取得できない可能性が高くなります。

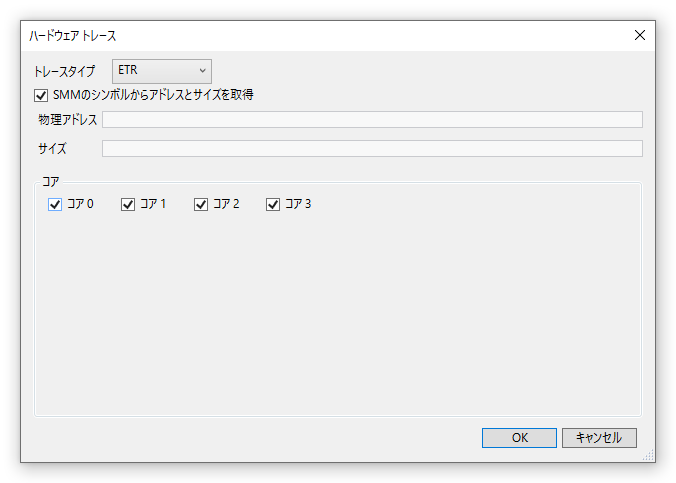

ETRの設定¶

ETRを使用する場合は、トレースデータをターゲット上のRAMに保存するため、その物理アドレスを指定する必要があります。 ここでは、メモリマップデザイナと連携する方法について解説します。

ハードウェアトレースの設定ダイアログで、 トレースタイプ を ETR に設定し、 SMMのシンボルからアドレスとサイズを取得 にチェックを入れます。

メモリマップデザイナと連携しない場合には、直接物理アドレスとサイズを指定してください。この場合、プログラムが使用するメモリ領域と重ならないように注意してください。

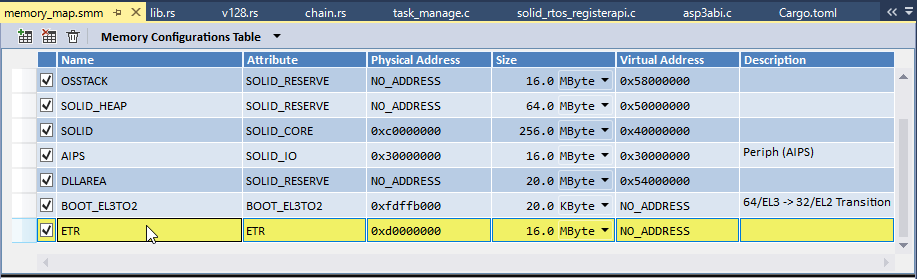

メモリマップデザイナに

ETRという名前でメモリ領域を作成し、AttributeもETRに設定します。 このとき、物理メモリを必ず指定してください。仮想アドレスはNO_ADDRESSで問題ありません。

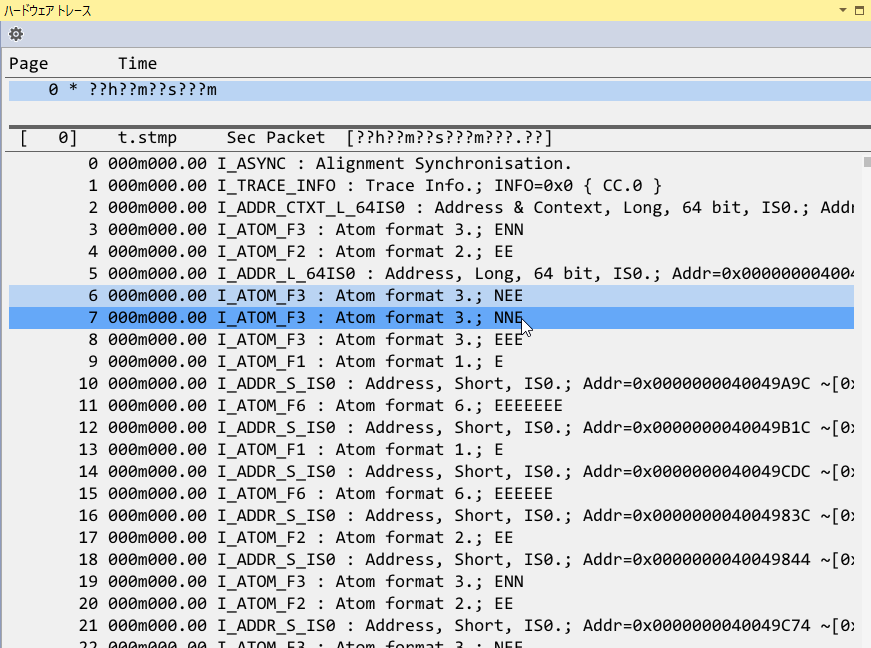

トレースデータの参照¶

デバッグを開始し、ブレーク後にメニューの からトレースウィンドウを開くと、 実行を開始してからブレークするまでの実行履歴(トレースパケット)のダンプ結果が表示されます。

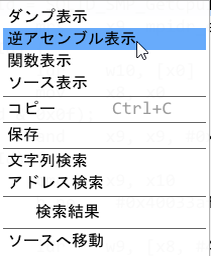

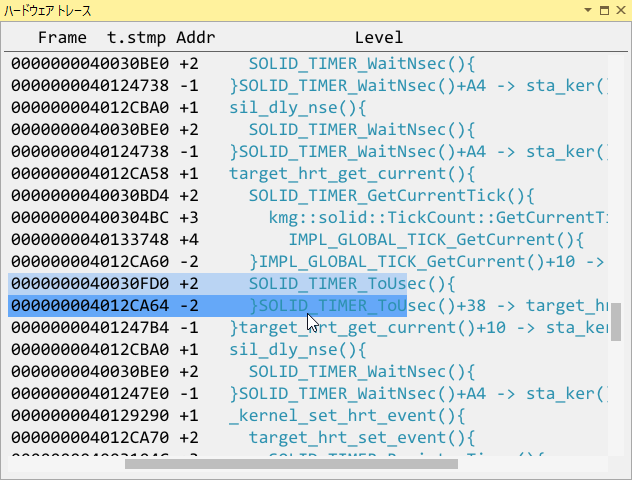

コンテキストメニューから、逆アセンブルや関数表示などを選択すると、表示を切り替えられます。

逆アセンブル表示¶

実行履歴を逆アセンブルで表示します。

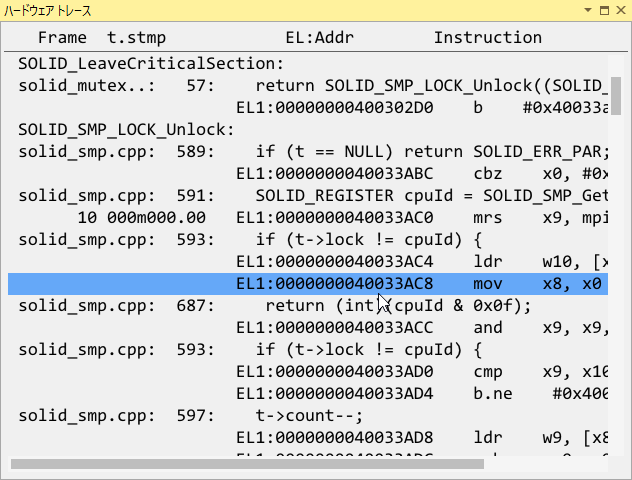

関数表示¶

関数の呼び出し履歴を表示します。

参考¶

ETBとETRの比較¶

ETB |

ETR |

|

|---|---|---|

取得可能なトレースの量 |

☓ |

○ |

オーバーフローの発生頻度 |

△ |

☓ |

ターゲットへの負荷 |

○ |

☓ |

設定の手間 |

○ |

△ |

ETBはCPUに内蔵されているトレース専用のメモリにトレースデータを保存するため、実行中のターゲットには影響をほぼ与えませんが、メモリサイズが小さい(8KB~64KB)ので、解析したい範囲が限定的な場合に向いています。

ETRはターゲットのRAMを使用するため、アドレスを設定(物理アドレス)する必要があります。また、DRAMコントローラが初期化される前には使用できません。

トレースのオーバーフローは、ターゲットプログラムの性質、トレースバスの帯域によって発生頻度が変化します。また、ETRの場合にはターゲットのメモリ帯域も影響します。

タイトなループを回っている場合(ブランチが多い場合)、トレースパケットのサイズが爆発しオーバーフローが発生する確率が高くなります。また、直接ブランチよりも間接ブランチが多い場合に発生しやすくなります。

トレースバスの帯域はターゲットとなるSoCに依存します。

ターゲットのメモリ帯域はSoCの他に、動作中のプログラムのメモリアクセス頻度も影響します。